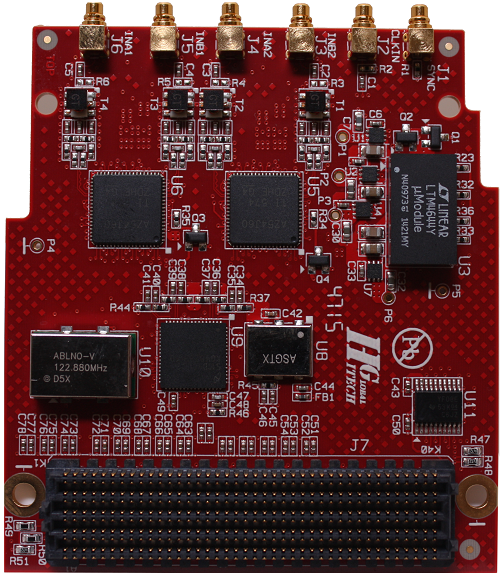

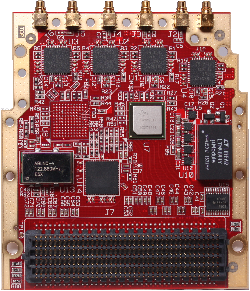

概要

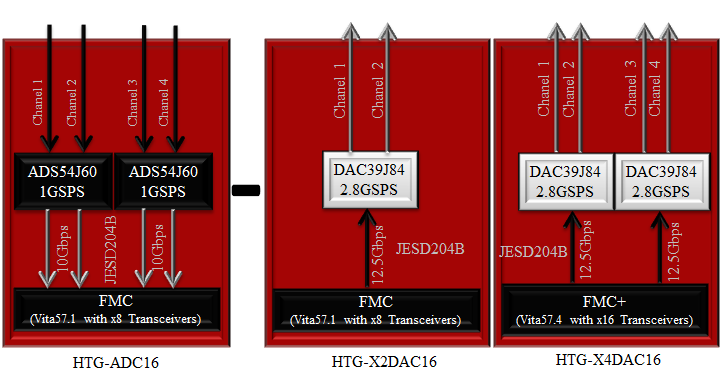

HiTech GlobalのHTG-ADC16およびHTG-DAC16 FMCモジュール/FMC+モジュールはVita 57.1もしくはVita 57.4準拠のFPGAキャリアボードのFMC HPCもしくはHSPCスロットに挿入されます。4つの16-bit ADCチャンネルと、2つ(FMC)もしくは4つ(FMC+)の16-bit DACチャンネルへのアクセスを提供しています。

4チャンネルDAC(16シリアルトランシーバを要求)はHTG-9100, HTG-830もしくはHTG-828などのVita 57.4準拠FPGAキャリアカードのみで動作します。これらのモジュールはJESD204B対応のTexas Instruments社デバイスを使用しています。

| 外観(4ch ADC) | 外観(2ch DAC) | 外観(4ch DAC) |

|---|---|---|

|

|

|

| ブロック図 | ||

|

||

AD Converter : HTG-ADC16 (ADS54J60搭載)

概要

ADS54J60は低消費電力な広帯域幅、16-bit, 1.0-GSPS, デュアルチャンネルのAnalog-to-digital converterです。 高いsignal-to-noise ratio (SNR)で設計されており、広い瞬時帯域幅にわたって最高のダイナミックレンジを目指すアプリケーションに対して-159 dBFS/Hzのノイズフロアを実現しています。 デバイスはADCあたり2つもしくは4つのレーンをサポートする最大データレート10.0GbpsのJESD204Bシリアルインターフェースを搭載しています。 Buffered analog inputは sample-and-holdグリッチエネルギを最小にし、幅広い周波数レンジにわたり一様な入力インピーダンスを実現しています。それぞれのADCチャンネルは、オプションでwideband digital down-converter(DDC) blockに接続することが可能です。 ADS54J60は非常に低い消費電力で、広い入力周波数レンジにわたって素晴らしいspurious-free dynamic range (SFDR)を提供します。

JESD204Bインターフェースはインターフェースラインの数を減らし、高いシステムインテグレーション密度を可能にします。それぞれのチャンネルから入力される16-bitデータをシリアル化するために使用されるビットクロックを得るために、内部phase-locked loop (PLL)がADCサンプリングクロックを逓倍します。

機能

- 16-Bit Resolution, Dual-Chanel, 1-GSPS ADC

- Noise Floor: -159 dBFS/Hz

- Spectral Performance (fIN = 170 MHz at –1 dBFS)

- SNR: 70 dBFS

- NSD: –157 dBFS/Hz

- SFDR: 86 dBc

- SFDR: 96 dBc (Except HD2, HD3, and Interleaving Tones)

- Spectral Performance (fIN = 350 MHz at –1 dBFS)

- SNR: 67.5 dBFS

- NSD: –154.5 dBFS/Hz

- SFDR: 75 dBc

- SFDR: 85 dBc (Except HD2, HD3, and Interleaving Tones)

- Channel Isolation: 100 dBc at fIN = 170 MHz

- Input Full-Scale: 1.9 VPP

- On-Chip Dither

- Integrated Wideband DDC Block

- JESD204B Interface with Subclass 1 Support

- 2 Lanes per ADC at 10.0 Gbps

- 4 Lanes per ADC at 5.0 Gbps

- Support for Multi-Chip Synchronization

- Power Dissipation: 1.35 W/ch at 1 GSPS

DA Converter : HTG-DAC16 (DAC39J84搭載)

概要

DAC39J84は非常に低消費電力でJESD204Bインターフェースを搭載した16-bit、クアッドチャンネル、2.8 GSPSのDigital-to-analog converterです。デジタルデータは1, 2, 4, 8本の設定可能なシリアルJESD204Bレーンでデバイスへ入力され、オンチップターミネーションおよびプログラマブルなイコライゼーションを使用し、それぞれが最大12.5Gbpsで動作します。このインターフェースにより、JESD204B Subclass 1 SYSREFベースなdeterministic latencyと複数デバイスの完全な同期を可能にしています。

デバイスは複雑なtransmit architectureの設計を簡素化する機能を含んでいます。完全にバイパス可能な、 90dBを超えるstop-band attenuationをもつ2xから16xまでのデジタル補間フィルタにより、データインターフェースとフィルタを簡素化できます。オンチップの48-bit Numericaly Controlled Oscillator (NCO)および独立したComplex Mixersにより、フレキシブルで正確なcarrier placementが可能です。

高性能な低ジッタPLLにより、ダイナミックレンジ上に大きな影響を及ぼすことなくデバイスのクロック設定を簡素化することができます。 digital Quadrature Modulator Correction (QMC)およびGroup Delay Correction (QDC)により、直接の昇圧変換アプリケーションにおいて、チャンネル間のゲイン、オフセット、位相およびグループ遅延の完全なIQ補償が可能になります。入力データに異常な電力動作が検出された場合に備えて、パワーアンプ(PA)を保護するためのプログラマブルなPA保護機構が利用可能です。

機能

- Resolution: 16-Bit

- Maximum Sample Rate: 2.8GSPS

- Maximum Input Data Rate: 1.25GSPS

- JESD204B Interface

- 8 JESD204B Serial Input Lanes

- NSD: –154.5 dBFS/Hz

- 12.5 Gbps Maximum Bit Rate per Lane

- Subclass 1 Multi-DAC Synchronization

- On-Chip Very Low Jitter PLL

- Selectable 1x –16x Interpolation

- Independent Complex Mixers with 48-bit NCO/ or ±n×Fs/8

- Wideband Digital Quadrature Modulator Correction

- Sinx/x Correction Filters

- Fractional Sample Group Delay Correction

- Multi-Band Mode: Digital Summation of Independent Complex Signals

- 3/4-Wire Serial Control Bus (SPI)

- Integrated Temperature Sensor

- JTAG Boundary Scan

- Pin-Compatible with Quad-Channel DAC37J84/ DAC38J84 Family

- Power Dissipation: 1.8W at 2.8GSPS(SPI)

注文情報

- HTG-FMC-ADS54-4 (4チャンネルADC Vita 57.1とVita 57.4キャリアボードに互換)

- HTG-FMC-DAC39-IQ2 (2チャンネルDAC Vita 57.1とVita 57.4キャリアボードに互換)

- HTG-FMC-DAC39-IQ4 (4チャンネルDAC Vita 57.4キャリアボードのみ対応)